# **Proximity Communication Interface Implementation Specifications**

Version 1.1

# **JULY 2001**

**New Media Development Association**

(foundational juridical person)

#### **Foreword**

The New Media Development Association has developed a "Development of Platform for New Generation Smart Card Systems" based on an innovative architecture that is able to accommodate new functional requirements and diverse security levels with the aim of systematically integrating the various card specifications in existence at present as a part of the "Industrial and Social Information Infrastructure Development Project" implemented by the Japan Information Processing Development Corporation in accordance with the third supplementary budget for the 1998 fiscal year. This development was carried out with particular focus on contactless IC cards --- proximity cards (PICC) as defined in ISO/IEC 14443 for which popularity is expected to grow in a wide range of IC card applications in the future. The "Proximity Communications Interface Implementation Specification" (Version 1.0) were released in December 2000 in the form of a disclosed technical reference that summarized the results of studies for improving compatibility between PICC and proximity coupling devices (PCD) based on experience acquired during the course of their development.

This specification is a revised version of the previous version 1.0. The following factors were taken into consideration in the production of this revised edition.

- Although Version 1.0 was produced on the basis of the latest documents available relating to ISO/IEC 14443 as of March 2000, since that time, work at ISO have progressed, and with some exceptions, were released in the form of ISO standards. It was therefore necessary to achieve compatibility with these ISO standards.

- Following the release of Version 1.0, requests were made from various fields asking for implementation specifications for PCD (open PCD) that will enable the operation of placing or holding up a card. Implementation specifications were therefore added or reviewed in order to respond to these needs.

We hope that this specification will assist in the future proliferation of IC cards and IC card systems.

Furthermore, be aware of the following when referring to or using these specifications.

- The functions, testing methods and so forth specified in these specifications are subject to addition, revision, alteration or deletion during the course of substantiative testing and other efforts scheduled to be conducted in the future by this association.

- This association is not responsible in any way for the contents of these specifications or the results of their use, including industrial property rights and so forth.

In conclusion, the association would like to express its deep appreciation to the RW compatibility verification work group (located within the New Media Development Association) for its numerous contributions and constructive discussions, and to those persons at the Ministry of Economics, Trade and Industry for their generous support of those efforts pertaining to the production of these specifications.

July 2001

New Media Development Association

### Table of contents

| 1. | SY         | STEM OVERVIEW                                        | 1    |

|----|------------|------------------------------------------------------|------|

| 2. | DE         | SIGN GUIDELINES                                      | 2    |

| 2  | .1         | Introduction                                         | 2    |

| 2  | .2         | CHARACTERISTICS OF ASSUMED PICC AND PCD              | 3    |

| 2  | .3         | CHARACTERISTICS OF THIS IMPLEMENTATION SPECIFICATION | 5    |

| 2  | .4         | DOMESTIC RADIO LAW                                   | 7    |

| 2  | .5         | CITED STANDARDS                                      | 8    |

| 2  | .6         | OTHERS                                               | 9    |

| 3. | Co         | OMPONENTS                                            | 10   |

| 4. | Us         | SAGE CONDITIONS                                      | 13   |

| 4  | .1         | BASIC GUIDELINES                                     | . 13 |

| 4  | .2         | BASIC CONDITIONS                                     | . 14 |

| 5. | CA         | ARD ANTENNA CHARACTERISTICS                          |      |

| 5  | .1         | Antenna Shape                                        | .16  |

| 5  | .2         | ANTENNA RESISTANCE VALUE                             | .17  |

| 5  | .3         | INDUCTANCE                                           | . 18 |

| 5  | .4         | RESONANCE FREQUENCY                                  | . 19 |

| 5  | .5         | MATERIAL AND PRODUCTION METHOD                       | .20  |

| 6. | CA         | ARD IC CHARACTERISTICS                               | 21   |

| 6  | .1         | Operating Power                                      | .21  |

| 6  | .2         | INPUT SIGNAL                                         | . 24 |

| 6  | .3         | OUTPUT SIGNAL                                        | .25  |

| 7. | PC         | CD Antenna Characteristics                           | 26   |

| 7  | .1         | ANTENNA POSITION                                     | .26  |

| 7  | .2         | Antenna Shape                                        | .27  |

| 7  | .3         | ANTENNA RESISTANCE VALUE                             | .28  |

| 7  | .4         | INDUCTANCE                                           | .29  |

| 7  | .5         | RESONANCE FREQUENCY                                  | .30  |

| 7  | .6         | MATERIAL AND PRODUCTION METHOD                       | .31  |

| 8. | Po         | WER TRANSMISSION                                     | 32   |

| 8  | .1         | Frequency                                            | .32  |

| 8  | .2         | OPERATING MAGNETIC FIELD                             | .33  |

|    | 8.2        | 1 0 0                                                |      |

| 0  | 8.2        |                                                      |      |

| 9. |            | OMMUNICATION PCD TO PICC                             |      |

| 9  | .1         | COMMUNICATION SIGNAL INTERFACE TYPE A                |      |

|    | 9.1        |                                                      |      |

|    | 9.1<br>9.1 |                                                      |      |

|    | 9.1        | Lo Du nepresentation and coung                       | აყ   |

| 9.2 Con    | MMUNICATION SIGNAL INTERFACE TYPE B                                     | 40   |

|------------|-------------------------------------------------------------------------|------|

| 9.2.1      | Bit Rate                                                                | 40   |

| 9.2.2      | Modulation                                                              | 41   |

| 9.2.3      | Bit Representation and Coding                                           | 42   |

| 10. COMM   | IUNICATION PICC TO PCD                                                  | . 43 |

| 10.1 Con   | MMUNICATION SIGNAL INTERFACE TYPE A                                     | 43   |

| 10.1.1     | Bit Rate                                                                |      |

| 10.1.2     | Load Modulation                                                         | 44   |

| 10.1.3     | Subcarrier                                                              | 45   |

| 10.1.4     | Subcarrier Modulation Method                                            | 46   |

| 10.1.5     | Bit Representation and Coding                                           | 47   |

| 10.2 Con   | MMUNICATION SIGNAL INTERFACE TYPE B                                     | 48   |

| 10.2.1     | Bit Rate                                                                | 48   |

| 10.2.2     | Load Modulation                                                         | 49   |

| 10.2.3     | Subcarrier                                                              | 50   |

| 10.2.4     | Subcarrier Modulation                                                   | 51   |

| 10.2.5     | Bit Representation and Coding                                           | 52   |

| 11. Pollin | NG                                                                      | . 53 |

| 12. Antic  | OLLISION                                                                | . 55 |

| 12.1 Typ   | E A-INITIALIZATION AND ANTICOLLISION                                    | 59   |

| 12.1.1     | Frame Format and Timing                                                 | 59   |

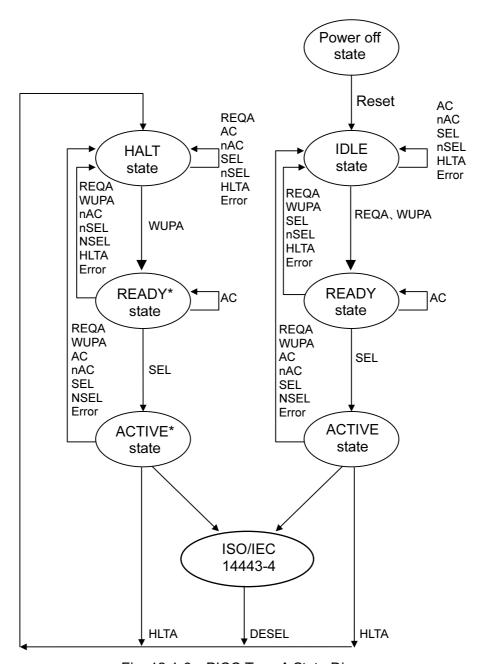

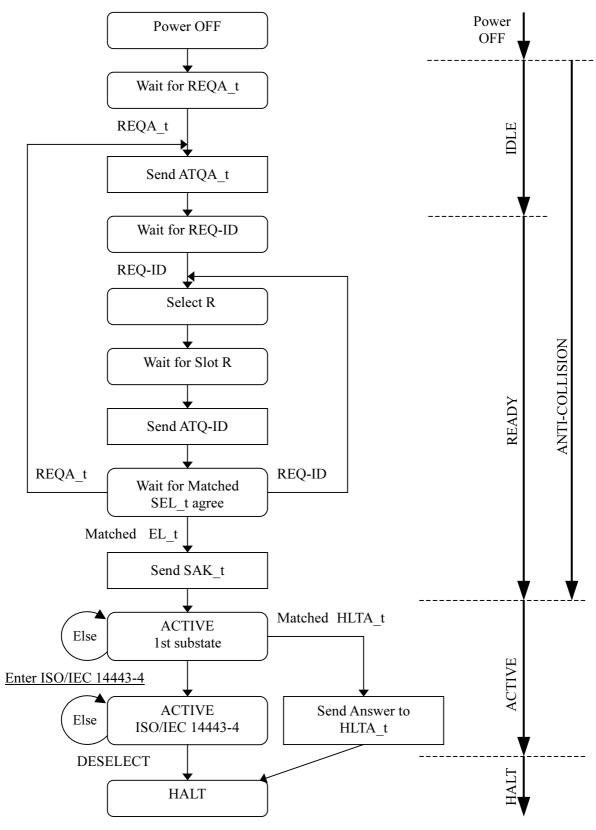

| 12.1.2     | PICC States                                                             |      |

| 12.1.3     | Command Set                                                             | 80   |

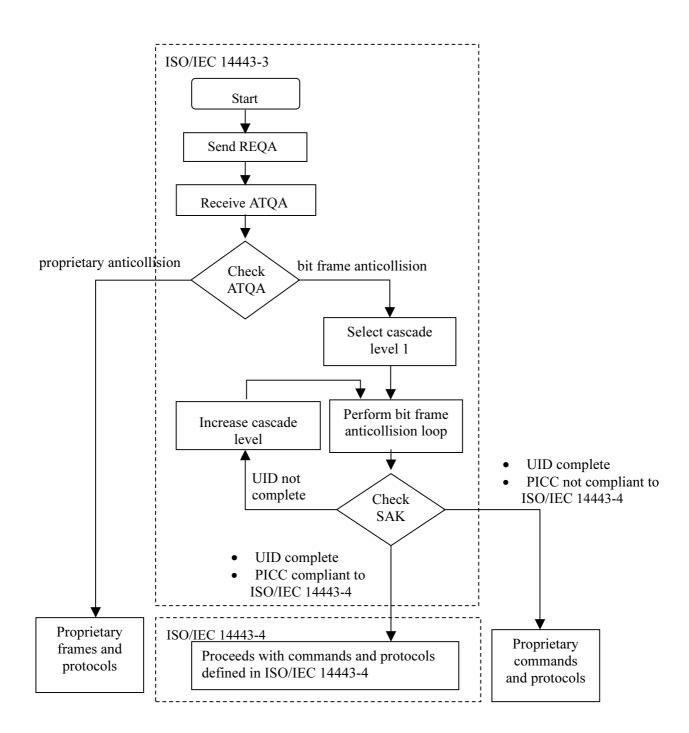

| 12.1.4     | Select Sequence                                                         | 84   |

| 12.2 Typ   | E B - INITIALIZATION AND ANTICOLLISON                                   | 99   |

| 12.2.1     | Character, Frame Format and Timing                                      |      |

| 12.2.2     | Cyclic Redundancy Check Code (CRC_B)                                    |      |

| 12.2.3     | Anticollision Sequence                                                  |      |

| 12.2.4     | PICC States Description                                                 | 109  |

| 12.2.5     | Command Set                                                             | 119  |

| 12.2.6     | Anticollision Response Rules                                            | 120  |

| 12.2.7     | REQB/WUPB Command                                                       | 122  |

| 12.2.8     | Slot Marker Command (Slot_MARKER)                                       | 129  |

| 12.2.9     | Answer to Request (ATQB)                                                | 132  |

| 12.2.10    | ATTRIB Command                                                          | 140  |

| 12.2.11    | Answer to ATTRIB Command                                                | 149  |

| 12.2.12    | HLTB Command and Answer                                                 | 151  |

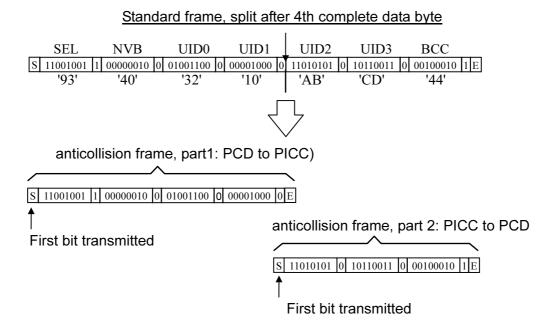

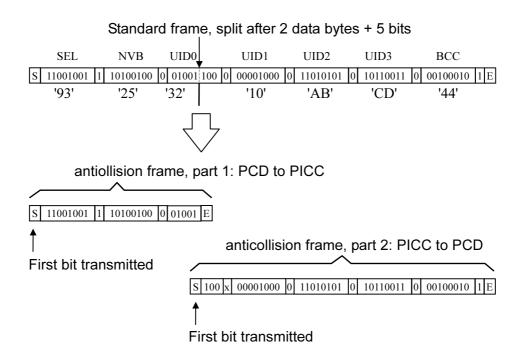

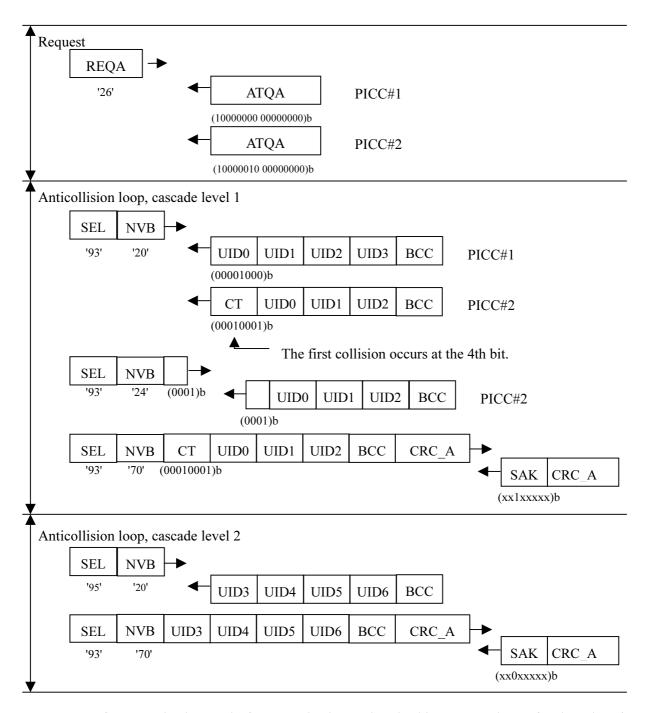

| 12.3 Con   | MMUNICATION EXAMPLE TYPE A                                              | 152  |

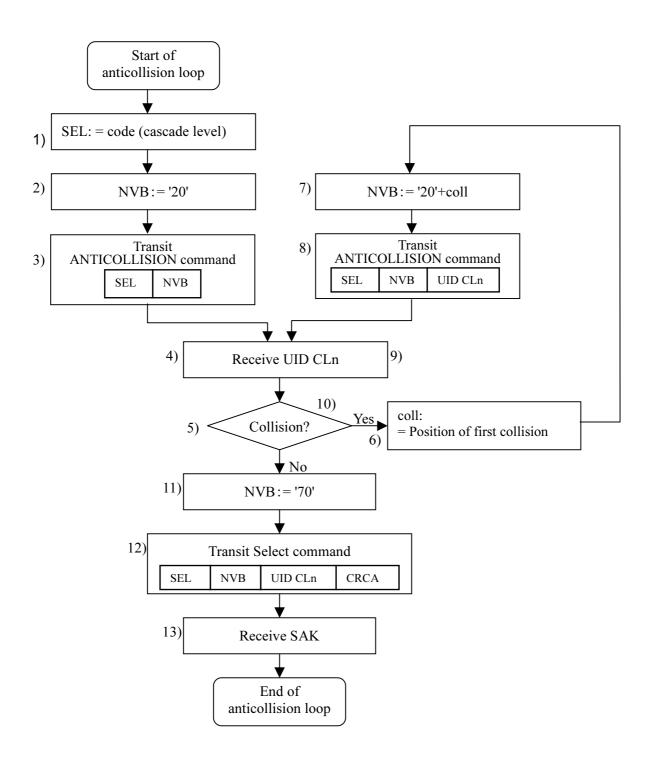

| 12.3.1     | Overview of Communication Example of Bit Frame Anticollision Processing | 152  |

| 12.3.2     | Explanation of Selection Processing of Bit Frame Anticollision          | 155  |

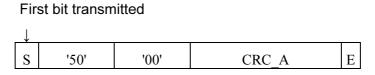

| 12.4 CRO   | C_A AND CRC_B ENCODING                                                  | 158  |

| 12.4.1     | CRC_A Encoding                                                          |      |

| 12.4.2     | CRC_B Encoding                                                          |      |

| 12.4.3     | Code Sample Written in C Language for CRC Calculation                   | 165  |

| 12.5 TYP  | PE A TIMESLOT - INITIALIZATION AND ANTICOLLISION       | 168 |

|-----------|--------------------------------------------------------|-----|

| 12.5.1    | Bit, Byte and Frame Format                             | 169 |

| 12.5.2    | PICC States                                            | 171 |

| 12.5.3    | Command/Response Sets                                  | 176 |

| 12.5.4    | Time Slot Type Anticollision Processing                | 179 |

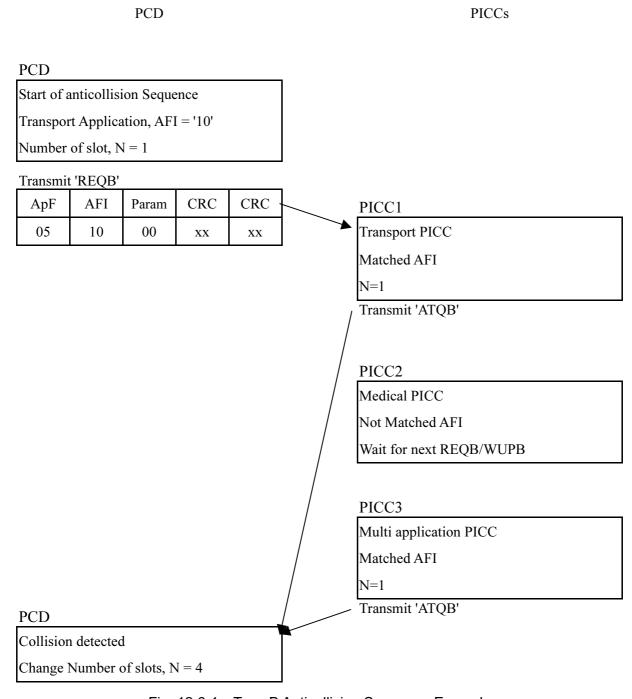

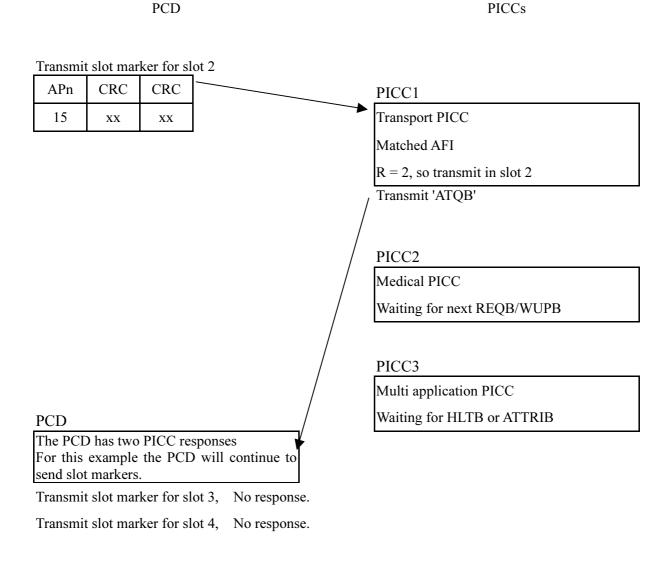

| 12.6 EXA  | AMPLE OF ANTICOLLISION SEQUENCE FOR TYPE B             | 182 |

| 13. TRANS | SMISSION PROTOCOL                                      | 187 |

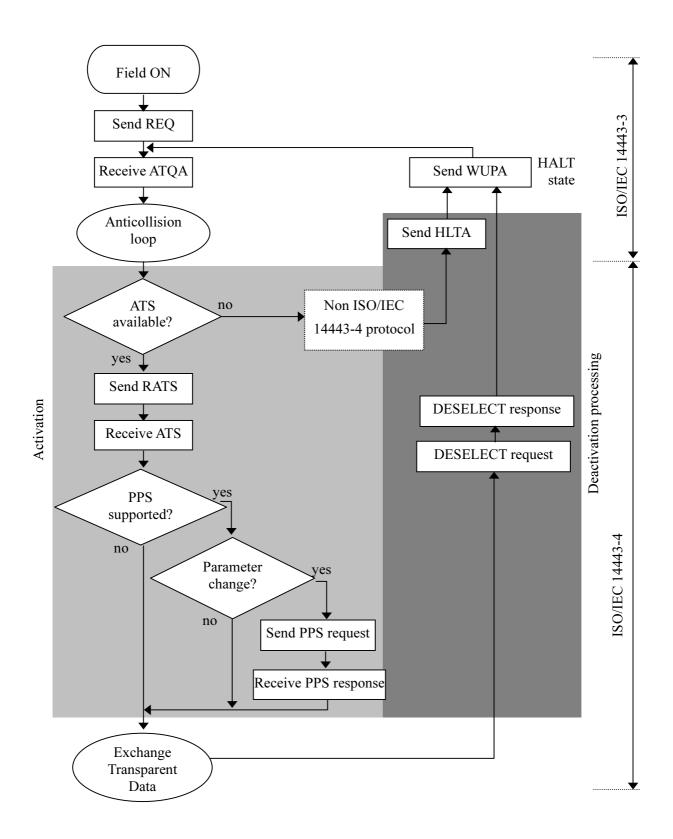

| 13.1 PRO  | OTOCOL ACTIVATION OF PICC TYPE A                       | 190 |

| 13.1.1    | Request for Answer to Select                           | 193 |

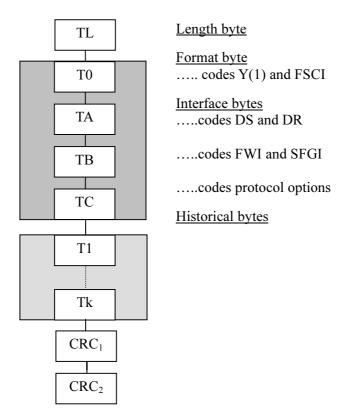

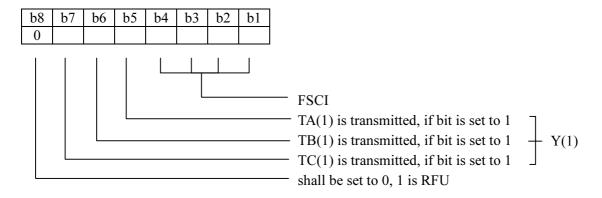

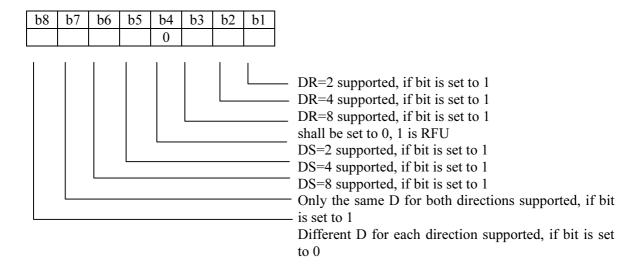

| 13.1.2    | Answer to Select (ATS)                                 | 195 |

| 13.1.3    | Protocol and Parameter Selection Request               | 203 |

| 13.1.4    | Protocol and Parameter Selection Response              | 207 |

| 13.1.5    | Activation Frame Waiting Time                          |     |

| 13.1.6    | Error Detection and Recovery                           | 209 |

| 13.2 PRO  | DTOCOL ACTIVATION OF PICC TYPE B                       | 212 |

| 13.3 HAI  | LF-DUPLEX BLOCK TRANSMISSION PROTOCOL                  | 213 |

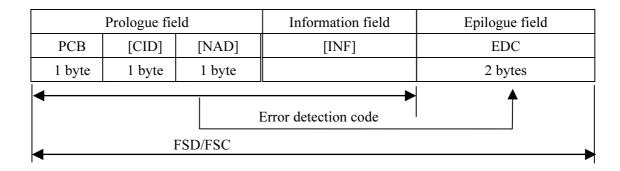

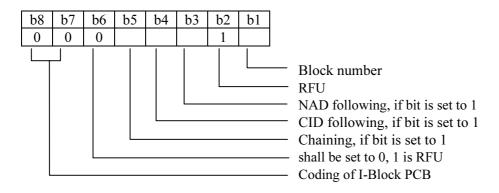

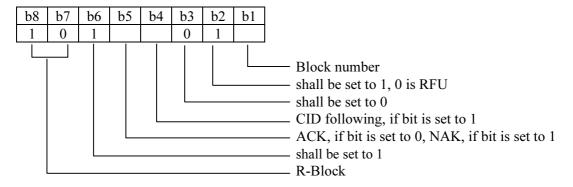

| 13.3.1    | Block Format                                           | 214 |

| 13.3.2    | Frame Waiting Time (FWT)                               | 221 |

| 13.3.3    | Power Level Indication                                 | 224 |

| 13.3.4    | Protocol Operation                                     | 225 |

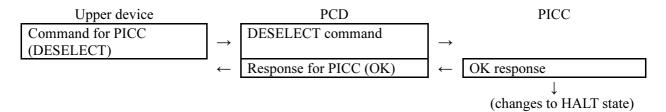

| 13.4 PRO  | OTOCOL DEACTIVATION OF PICC TYPE A AND TYPE B          | 233 |

| 13.4.1    | Deactivation Frame Waiting Time                        | 234 |

| 13.4.2    | Error Detection and Recovery                           | 235 |

| 13.5 Mu   | LTI-ACTIVATION EXAMPLE                                 | 236 |

| 13.6 PRO  | OTOCOL SCENARIOS                                       | 237 |

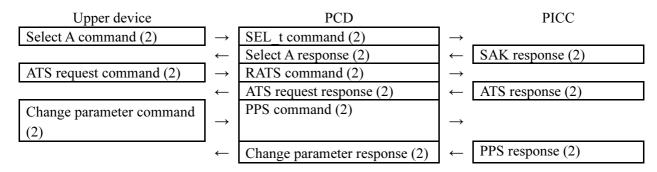

| 13.6.1    | Error-free Operation                                   | 239 |

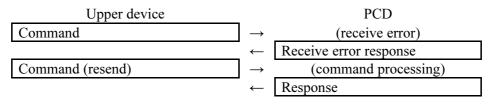

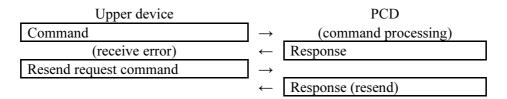

| 13.6.2    | Error handling                                         | 243 |

| 13.7 BL0  | OCK AND FRAME CODING OVERVIEW                          | 252 |

| 13.8 T=1  | PROTOCOL USAGE SPECIFICATIONS                          | 254 |

| 13.8.1    | PICC Activation                                        |     |

| 13.8.2    | Protocol Processing                                    |     |

|           | ANSMISSION CONTROL MATRIX OF T=CL PROTOCOL (REFERENCE) |     |

|           | TEST METHODS                                           |     |

|           | T ENVIRONMENT                                          |     |

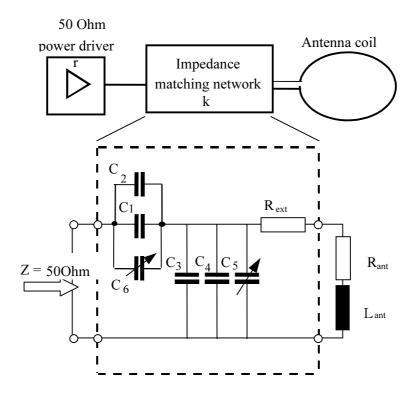

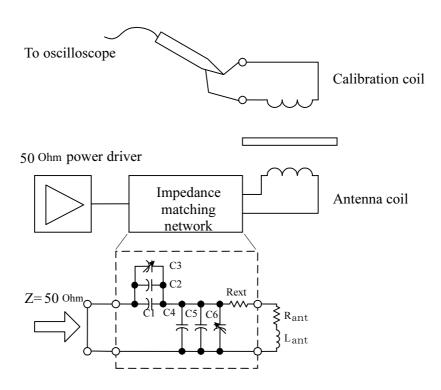

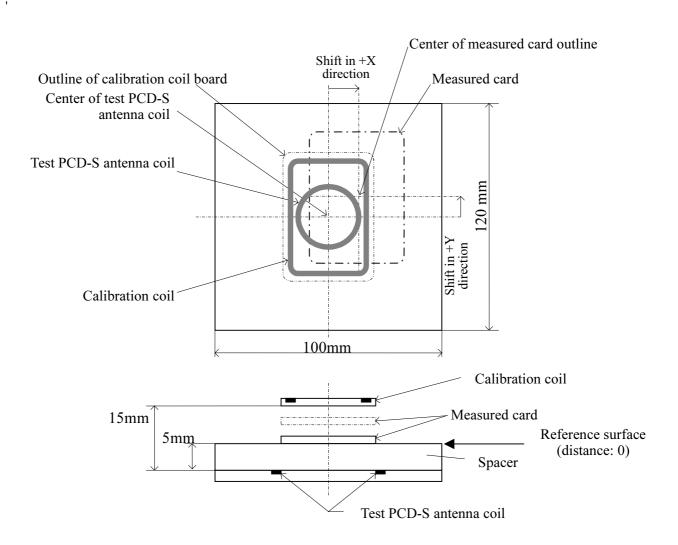

|           | T APPARATUS                                            |     |

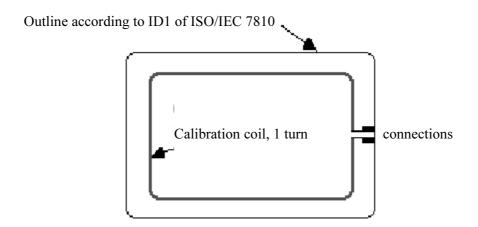

| 14.2.1    | Calibration Coil                                       |     |

| 14.2.2    | Test PCD                                               |     |

| 14.2.3    | Test PCD-S                                             |     |

| 14.2.4    | Digital Sampling Oscilloscope                          |     |

|           | T METHODS                                              |     |

| 14.3.1    | Testing Using Test PCD                                 |     |

| 14.3.2    | Testing Using Test PCD-S                               |     |

|           | From Memuone                                           | 200 |

| 15.1 TE    | ST ENVIRONMENT                                         | 299 |  |  |

|------------|--------------------------------------------------------|-----|--|--|

| 15.2 TE    | ST APPARATUS                                           | 300 |  |  |

| 15.2.1     | Reference PICC                                         | 301 |  |  |

| 15.3 Tes   | ST METHODS                                             | 312 |  |  |

| 15.3.1     | Magnetic Field Strength                                | 312 |  |  |

| 15.3.2     | Power Transmission Test                                | 316 |  |  |

| 15.3.3     | Modulation Waveform                                    | 318 |  |  |

| 15.3.4     | Reception Ability of Load Modulation Signal            | 320 |  |  |

| 16. EXTE   | RNAL COMMUNICATION PROTOCOL                            | 322 |  |  |

| 16.1 Рн    | YSICAL INTERFACE                                       | 322 |  |  |

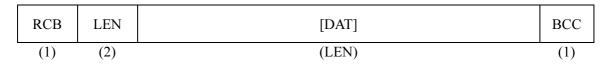

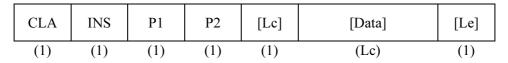

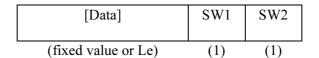

| 16.2 BL    | OCK FORMAT                                             | 324 |  |  |

| 16.2.1     | RCB (Required)                                         | 325 |  |  |

| 16.2.2     | LEN (Required)                                         | 326 |  |  |

| 16.2.3     | DAT (Optional)                                         | 327 |  |  |

| 16.2.4     | BCC (Required)                                         | 328 |  |  |

| 16.3 Co    | MMUNICATION TIME SPECIFICATIONS                        | 329 |  |  |

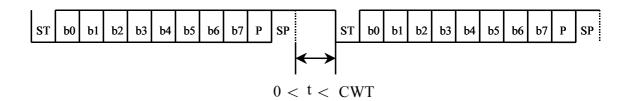

| 16.3.1     | Character Waiting Time (CWT)                           | 330 |  |  |

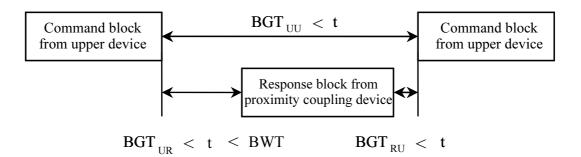

| 16.3.2     | Block Guard Time (BGT)                                 | 331 |  |  |

| 16.3.3     | Block Waiting Time (BWT)                               | 332 |  |  |

| 16.4 Co    | MMUNICATION ERROR PROCESSING                           | 333 |  |  |

| 16.4.1     | PCD Communication Error Processing                     | 333 |  |  |

| 16.4.2     | Upper Device Communication Error Processing            | 335 |  |  |

| 16.5 Co    | MMANDS AND RESPONSES                                   | 337 |  |  |

| 16.5.1     | Commands and Response for PICC                         | 337 |  |  |

| 16.5.2     | Summary of Commands and Responses for PCD              | 340 |  |  |

| 16.5.3     | Details of Commands and Responses for PCD.             | 344 |  |  |

| 16.6 RE    | FERENCE INFORMATION                                    | 377 |  |  |

| 16.6.1     | Normal Communication Sequence Examples                 | 377 |  |  |

| 16.6.2     | Abnormal Communication Sequence Example                | 382 |  |  |

| 17. Com    | PATIBILITY TEST METHOD                                 | 388 |  |  |

| [REFERENCE | REFERENCE] EXAMPLE OF COMPATIBILITY VERIFICATION SHEET |     |  |  |

### 1. System Overview

These proximity communication interface implementation specification define specifications and standards that supplement ISO/IEC 14443-2, 3 and 4 with respect to functions pertaining to contactless communication between the PICC and PCD. Therefore, these specifications attempt to ensure interoperability and compatibility of various types of PICCs and PCDs of numerous manufacturers by serving to standardize antenna characteristics, resonance characteristics and various other parameters at the production level not defined by ISO.

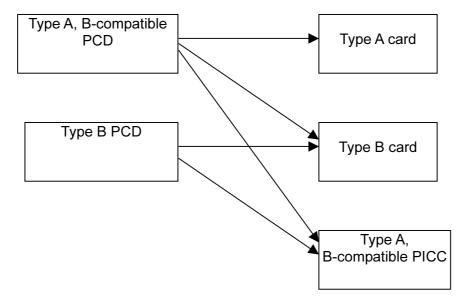

These implementation specifications apply to PICC based on the radio wave interface type of ASK 100% modulation type A or ASK 10% modulation type B as indicated in ISO/IEC 14443-2 as well as PCD capable of operating both of these cards.

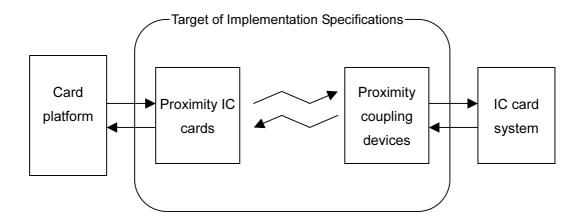

The range over which this implementation specification are applicable is shown in "Fig. 1-1 Target of Proximity Communication Interface Implementation Specifications".

Fig. 1-1 Target of Proximity Communication Interface Implementation Specifications

### 2. Design Guidelines

#### 2.1 Introduction

Proximity communication interface implementation standards are produced to ensure interoperability and compatibility between PICC and PCD under specific usage conditions indicated in "4. Usage Conditions". These are discussed in ISO/IEC specifications (ISO/IEC 14443 PICC Specifications) so as not to inhibit the extendability and diversity of usage conditions. Accordingly, it is necessary to add to and alter ISO/IEC specifications in order to ensure compatibility based on the premise of certain specific usage conditions.

To begin with, in this implementation specification, ISO/IEC specifications are defined and described as "Basic Specifications" in the sense of serving as the basis of this implementation specification.

Next, specifications that are added in the form of implementation specifications are defined and described as "Extended Specifications" in the sense of being an extension to the basic specifications.

Moreover, those specifications not included in "basic specifications" or "extended specifications" for which implementation is preferable but not required are defined and described as "References".

#### 2.2 Characteristics of Assumed PICC and PCD

The IC card systems assumed in these implementation specifications are characterized by enhanced security functions for which there are new needs with respect to PICC. Consequently, it is necessary to consider the matters indicated below.

#### (1) PICC Equipped with an Encryption Coprocessor

When implementing encryption processing such as public key encryption (ex. RSA) within an IC card, the current technology calls for an independent encryption coprocessor within the card IC for processing. This IC requires power consumption of roughly 50 mW or more. In this case, it is estimated that at least 100 mW will be required for the output of the PCD.

While a communication distance of about 10 cm is said to be required in the case of ticket gates of transportation means, it is not easy to achieve this communication distance with a PICC having power consumption of 50 mW or more. However, since there is a considerable likelihood that IC power consumption will be reduced and revisions will be made to domestic the Radio related law in the future, there is a possibility that communication distance will increase. Thus, it is necessary to specify the antenna size of the PICC with the potential for future development in mind. In order to achieve longer communication distances, it will be desirable to specify antenna sizes to be as large as possible.

#### (2) Single Card Operation and Two Card Operation

In the case of PICC, there are two possible operating forms: namely, an operating form in which only a single PICC communicates with a single PCD in the same manner as conventional contact IC cards (single card operation), and an operating form in which multiple PICCs establish links with a single PCD to communicate with that device (multiple card operation). Specifically, when the number of cards in multiple card operation is limited to two cards, it is referred to as a two card operation.

Single card operation is used in systems premised on processing with a single specific card. Two card operation is used in systems in which a PCD simultaneously establishes a link with two PICCs and uses each card for different roles, such as using the first PICC for a specific application, and the second PICC for payment for instance.

Caution is required in that, depending on which of these operation forms is assumed, the resonance frequency of the PICC and other design conditions vary. Although a PICC inherently premised on two card operation can also be used for single card operation enabling it to cover both forms of operation, since a system with the longest communication distance as possible may be implemented on the premise of single card operation, this implementation specification allows both PICC premised on single card operation and PICC premised on two card operation.

#### (3) Open PCD

In the case of contactless applications, received power basically decreases the farther away from the antenna. If an encryption coprocessors requiring large power consumption is loaded, with the present level of technology, it is necessary to bring the card close to the PCD. In such cases as well, from the viewpoint of ease of operation and ease of maintenance of the PCD, there is a desire to simply place or hold the card near the PCD without actually inserting the card into the slot of the PCD. A system mounted with an open PCD is preferable for such needs.

It is necessary for the PCD to comply with the existing domestic Radio laws for each of its antenna outputs (see "2.4 Domestic Radio Law"). Assuming the power consumption of a card IC to be about 50 mW, the PCD is assumed to be a premises radio station or convenience radio station.

If reductions in power consumption of card ICs progress and the output of PCD falls below 50 mW in the future, it may be possible to realize PCD that function as radio stations that do not require a license as with extremely low power radio stations.

#### (4) Slot-In Type PCD

Even with PICCs, in cases in which card processing requires a relatively long period of time at government offices and financial institutions, for example, in order to perform processing reliably, there have been requests from users indicating the desire to perform card processing with the card slipped into the PCD. In such cases, a system implemented with a slot-in type of PCD will be reguired.

When considering the convenience of performing official clerical procedures by users, it is desirable to suppress the antenna output to the range of extremely low power radio and use as an extremely low power radio station. However, with the slot-in type PCD, while supplying the required power to the card inside the PCD, the entire PCD is shielded thereby avoiding radiation outside the PCD and making it possible to suppress the output of radio waves to the outside for the entire PCD to within the range of an extremely low power radio station.

### 2.3 Characteristics of This Implementation Specification

The matters indicated below have been taken into consideration in this implementation specification.

### (1) Improvement of Compatibility of between PICCs and PCDs

This implementation specification were produced for the purpose of improving compatibility between PICC and PCD as indicated in "2.2 Characteristics of Assumed PICC and PCD". However, considerations have also been given to allow a certain degree of freedom in the design of PICC and PCD. It should therefore be noted that this implementation specification does not unequivocally guarantee the compatibility of PICC and PCD. In order to guarantee compatibility, users of this implementation specification expected to perform the PICC and PCD test methods indicated in Chapters 14 and 15, along with the operation tests for PICC and PCD actually used in the IC card system to be applied.

#### (2) Need for Specifications other than ISO/IEC Standards

ISO/IEC standards specify specifications oriented toward maintaining higher levels of extendability (or diversity). In addition, discussions are presented focusing mainly on remote functions. Consequently, the operating specifications of a PICC are specified as, for example, "Shall operate as intended in a magnetic field from 1.5 A/m to 7.5 A/m". The antenna diameter of the test PCD is 15 cm and also is premised to a certain extent on remote functions. In addition, the fact that specifications are basically based on magnetic field strength suggests that these standards are premised on that the PICC and PCD being arranged at a distance at which they do not exert mutual effects, and that a uniform magnetic field be formed.

In contrast, since this project assumes power consumption of the card IC to be around 50 mW, the PICC and PCD are arranged in a relationship such that they are in close physical proximity and that they mutually affect the physical and electrical characteristics of the antenna. It is extremely unlikely that the measuring instrument with a uniform magnetic field is identical to the actual magnetic field detected by the PICC. This point is not specified in ISO/IEC standards, and is the most characteristic point of this implementation specification.

### (3) Required Specifications other than ISO/IEC Standards

It is necessary to add the matters indicated below not described in ISO/IEC standards for the reasons described in the previous section. In other words, these are the important points of this implementation specification.

(a) PICC specifications (antenna shape, etc.)

See "5. Card Antenna Characteristics".

(b) Reference (surface reading type) PCD specifications for evaluation of PICC

See "14. Card Test Methods".

(c) PCD specifications (antenna shape, etc.)

See "7. PCD Antenna Characteristics ".

(d) Reference PICC specifications for evaluation of PCD

See "15. PCD Test Methods ".

(e) Protocol between external devices and PCD (reference specifications)

See "16. External Communication Protocol".

### 2.4 Domestic Radio Law

For reference purposes, the relationship between radio stations and power consumption for a frequency of 13.56 MHz in Japan is shown in "Table 2.4-1 References: Domestic Radio Stations (13.56 MHz  $\pm$  7 KHz) Rules and Power Consumption ".

Table 2.4-1 References: Domestic Radio Stations (13.56 MHz  $\pm$  7 KHz) Rules and Power Consumption

|                                                                                               | Extremely low power radio stations                                | Premise radio stations or convenience radio stations                                                                    | Specified low power                                                        |

|-----------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

| Rule                                                                                          | 54 dBmV/m or less (at 3 m) (Antenna output about 50 mW or less*1) | Antenna output 1 W or less<br>(equal to extremely low<br>power radio stations<br>outside the 13.56 MHz ± 7<br>KHz band) | Antenna output<br>10 mW                                                    |

| Power consumption                                                                             | Radio license not required                                        | Technical competence required, radio station application required                                                       | Technical<br>competence required,<br>radio station license<br>not required |

| Current example: No CPU Power consumption: 2-5 mW                                             | About several cm                                                  | About 10 cm                                                                                                             | About 5 mm                                                                 |

| PICC<br>Power consumption: 10-20<br>mW                                                        | About 5 mm (surface reading)                                      | About several cm                                                                                                        | Not possible                                                               |

| New generation IC card<br>CPU + encryption coprocessor<br>Power consumption: 25 mW or<br>more | About 5 mm<br>(surface reading)<br>shielded                       | -                                                                                                                       | Not possible                                                               |

<sup>\*1:</sup> Reference value assuming an antenna diameter of 30 mm

### 2.5 Cited Standards

The standards cited in these implementation specifications are indicated in "Table 2.5-1 Cited Standards".

Table 2.5-1 Cited Standards

| Standard number                          | Title                                                       | Publication   |

|------------------------------------------|-------------------------------------------------------------|---------------|

| ISO/IEC 14443-1                          | Identification cards-Contactless                            | First edition |

|                                          | integrated circuit (s) cards                                | 2000-04-15    |

|                                          | - Proximity cards -                                         |               |

|                                          | Part1: Physical characteristics                             |               |

| ISO/IEC 14443-2                          | Identification cards-Contactless                            | FDIS          |

|                                          | integrated circuit (s) cards                                | 2000-05-02    |

|                                          | - Proximity cards - Part2 : Radio                           |               |

|                                          | frequency power and signal interface                        |               |

| ISO/IEC 14443-3                          | Identification cards-Contactless                            | First edition |

|                                          | integrated circuit (s) cards                                | 2001-02-01    |

|                                          | - Proximity cards                                           |               |

|                                          | Part3: Initialization and anticollision                     |               |

| ISO/IEC 14443-4                          | Identification cards-Contactless                            | First edition |

|                                          | integrated circuit (s) cards                                | 2001-02-01    |

|                                          | - Proximity cards                                           |               |

|                                          | Part4: Transmission protocol                                |               |

| ISO/IEC 10373-6                          | Identification cards - Test methods -                       | FDIS          |

|                                          | Part4: Proximity cards                                      | 2001-01-18    |

| ISO/IEC 7810                             | Identification cards - Physical                             | 2nd edition   |

|                                          | characteristics                                             | 1995-08-15    |

| ISO/IEC 7816-2                           | ISO/IEC 7816-2 Identification cards - Integrated circuit(s) |               |

| cards with contacts - Part2 : Dimensions |                                                             | 1999-03-01    |

|                                          | and location of the contacts                                |               |

### 2.6 Others

Dimensions and values not having tolerances described in this implementation specification are treated as reference dimensions or reference values, and refer to the target central dimension and central value.

#### 3. Components

This Proximity Communication Interface Implementation Specification stipulate specifications and standards that supplement ISO/IEC 14443-2, 3 and 4 with respect to functions relating to contactless communications in PICC and external nodes.

This implementation specification applies to PICC based on the radio wave interface type of ASK 100% modulation type A or ASK 10% modulation type B indicated in ISO/IEC 14443-2, as well as PCD capable of operating both of these cards.

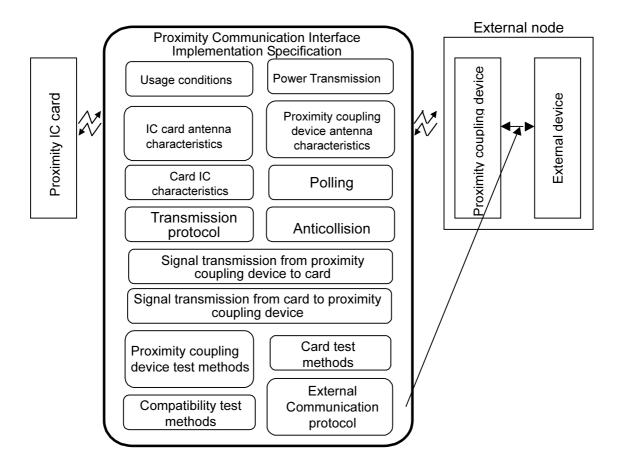

The components of this proximity communication interface implementation specification is indicated in "Fig. 3-1 Components of the Proximity Communication Interface Implementation Specification".

Fig. 3-1 Components of the Proximity Communication Interface Implementation Specification

The sub-categories in the main category of "Proximity Communication Interface Implementation Specification" are specified in "Table 3-1 Functional Components".

Table 3-1 Functional Components

| Chapter Title                | Description                                                                   |  |

|------------------------------|-------------------------------------------------------------------------------|--|

| Usage Conditions             | Specifies the usage conditions of the proximity communication                 |  |

|                              | interface assumed in applications. The specified usage conditions             |  |

|                              | include communication range, number of cards used, type of card               |  |

|                              | used and applicable radio law.                                                |  |

| Card Antenna Characteristics | Antenna shape, antenna resistance value and other characteristics             |  |

|                              | are specified as PICC antenna characteristics. Antenna                        |  |

|                              | characteristics are to be specified with difference in characteristics        |  |

|                              | due to antenna material and production method in mind.                        |  |

| Card IC Characteristics      | Characteristic values including IC power consumption and operating            |  |

|                              | voltage are specified as IC characteristics for PICC. IC                      |  |

|                              | characteristics are to be specified with difference in characteristics        |  |

|                              | due to IC function and production method in mind.                             |  |

| PCD Antenna Characteristics  | Antenna position, shape and other characteristics are specified as            |  |

|                              | PCD antenna characteristics. Antenna characteristics are to be                |  |

|                              | specified with differences in characteristics due to communication            |  |

|                              | performance and production method in mind.                                    |  |

| Power Transmission           | In addition to specifying power transmission characteristics of the           |  |

|                              | PCD based on ISO/IEC 14443-2, power transmission characteristics              |  |

|                              | of the PCD are specified in consideration of the PCD characteristics          |  |

|                              | and card characteristics as specified in these implementation specifications. |  |

| Signal Transmission from     | The modulation method, modulation waveform and encoding                       |  |

| PCD to Card                  | method of signal transmission from the PCD to the PICC are                    |  |

|                              | specified on the basis of ISO/IEC 14443-2. Type A and Type B                  |  |

|                              | communication methods are specified.                                          |  |

| Signal Transmission from     | The modulation method and encoding method of signal transmission              |  |

| Card to PCD                  | from the PICC to the PCD are specified on the basis of ISO/IEC                |  |

|                              | 14443-2. Type A and Type B communication methods are                          |  |

|                              | specified.                                                                    |  |

| Polling                      | Polling is specified based on ISO/IEC 14443-3 as a method for                 |  |

|                              | detecting whether or not a PICC capable of communicating with the             |  |

|                              | PCD is present. Polling methods are specified that are compatible             |  |

|                              | with both type A and type B communication methods.                            |  |

Table 3-1 Functional Components (continued)

| Chapter Title              | Description                                                         |  |  |

|----------------------------|---------------------------------------------------------------------|--|--|

| Anticollision              | Anticollision avoidance is specified on the basis of ISO/IEC        |  |  |

|                            | 14443-3 for acquiring identification information of PICC even when  |  |  |

|                            | multiple PICCs capable of communicating with the PCD are            |  |  |

|                            | present. Communication methods are specified for both type A and    |  |  |

|                            | type B. The method for type A is to be the time slot method.        |  |  |

| Transmission Protocol      | Communication frames and the basic communication sequence are       |  |  |

|                            | specified with the transmission protocol of the PICC and PCD on     |  |  |

|                            | the basis of ISO/IEC 14443-4. Type A and Type B communication       |  |  |

|                            | formats are specified.                                              |  |  |

| Card Test Methods          | Specifies the PICC test methods specified with ISO/IEC 10373-6,     |  |  |

|                            | while also specifying the test method of PICC in consideration of   |  |  |

|                            | the characteristics and so forth of the PCD as specified in this    |  |  |

|                            | implementation specification for the purpose of evaluating PICC.    |  |  |

| PCD Test Methods           | In addition to specifying test methods of the PCD based on ISO/IEC  |  |  |

|                            | 10373-6, test methods of the PCD are specified in consideration of  |  |  |

|                            | PICC characteristics specified in this implementation specification |  |  |

|                            | for the purpose of evaluating the PCD.                              |  |  |

| External Communication     | Commands and responses required for realizing a proximity           |  |  |

| Protocol                   | communication interface in the communication protocol between       |  |  |

|                            | the PCD and an external device are specified. Type A and type B     |  |  |

|                            | communication formats are specified. The method for type A is to    |  |  |

|                            | be the time slot method.                                            |  |  |

| Compatibility Test Methods | The test method is specified for evaluating interoperability and    |  |  |

|                            | compatibility of a PICC and PCD. The contents of evaluation by      |  |  |

|                            | cross-testing the PICC and PCD are also specified.                  |  |  |

### 4. Usage Conditions

The following specifies the usage conditions of the proximity communication interface assumed in this implementation specification. The specified usage conditions include communication range, number of cards used, type of card used and applicable radio telegraphy law.

#### 4.1 Basic Guidelines

Basic guidelines for drafting the usage conditions are indicated below.

- (1) Basic conditions are assumed with the focus on ensuring the safety of personal authorization such as issuing/confirmation of certificates and reserving/using public facilities as examples of applications in public fields.

- (2) PICC are assumed to be proximity contactless type cards that comply with ISO/IEC 14443 and which have a built-in chip containing a CPU and encryption coprocessor.

- (3) The electromagnetic waves generated from the PCD are assumed to be within the range of extremely low power radio waves in the case of slot-in PCD. In the case of open PCD, considering the current level of technology, the electromagnetic waves generated from the PCD are assumed to constitute an output that exceeds extremely low power radio waves.

# 4.2 Basic Conditions

Basic conditions relating to usage conditions are indicated in "Table 4.2-1 Basic Conditions".

Table 4.2-1 Basic Conditions

| No. | Item         | Description                                                                   |  |

|-----|--------------|-------------------------------------------------------------------------------|--|

| 1   | Usage form   | The following two usage forms are assumed.                                    |  |

|     |              | (1) Card is placed or held over the PCD (in the case of an open PCD).         |  |

|     |              | (2) Card is inserted into a slot or box equipped on the PCD (in the case of   |  |

|     |              | a slot-in PCD).                                                               |  |

|     |              | In either case, the direction of card insertion or orientation of the card is |  |

|     |              | not significant.                                                              |  |

| 2   | Type of PICC | The following two types are assumed.                                          |  |

|     |              | (1) Type A specified in ISO/IEC 14443-2                                       |  |

|     |              | (2) Type B specified in ISO/IEC 14443-2                                       |  |

| 3   | No. of cards | Only one card is assumed in the case of PICC premised on single card          |  |

|     | operated     | operation. One to two cards are assumed in the case of PICC premised          |  |

|     |              | on two card operation. However, the operated PICCs working in                 |  |

|     |              | combination are assumed to be of the same type (type A cards or type B        |  |

|     |              | cards), and operation of combinations of different types of cards is not      |  |

|     |              | specified in this implementation specification.                               |  |

| 4   | Applicable   | Shall be based on the Radio Law applied in Japan.                             |  |

|     | radio law    |                                                                               |  |

Table 4.2-1 Basic Conditions (continued)

| No. | Item           | Description                                                                   |  |

|-----|----------------|-------------------------------------------------------------------------------|--|

| 5   | Communication  | A distance of 0-5 mm (*1) and dislocation diameter of about 5 mm (*2)         |  |

|     | range          | are assumed in the case of slot-in PCD, while a distance of 0-20 mm and       |  |

|     |                | dislocation diameter of about 20 mm are assumed in the case of open           |  |

|     |                | PCD. However, this does not exclude communication outside this range.         |  |

|     |                | Furthermore, if held within holders (or other containers that hold the card), |  |

|     |                | the range shall be within such holder.                                        |  |

|     |                |                                                                               |  |

|     |                | *1: Distance refers to the distance to the surface opposing the PCD side of   |  |

|     |                | the PICC assuming the surface of the PCD casing to be 0 mm (origin) and       |  |

|     |                | the antenna of the PICC and the PCD are held horizontally.                    |  |

|     |                |                                                                               |  |

|     |                | *2 Dislocation refers to the amount of dislocation in the horizontal          |  |

|     |                | direction of the PICC assuming the reading center of the PCD and center       |  |

|     |                | of the outer diameter of the PICC are aligned to be 0 mm (origin) and the     |  |

|     |                | antenna of the PICC and the PCD are held horizontally.                        |  |

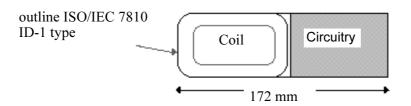

| 6   | PICC physical  | Shall be ID-1 specified in ISO/IEC 14443-1. However, thickness less           |  |

|     | specifications | than or equal to ID-1 are also allowed.                                       |  |

#### 5. Card Antenna Characteristics

Antenna shape, antenna resistance value and other characteristics are specified as PICC antenna characteristics. Antenna characteristics shall be specified with consideration to differences in characteristics due to antenna material and production methods.

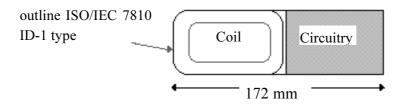

#### 5.1 Antenna Shape

#### (1) Basic Specifications

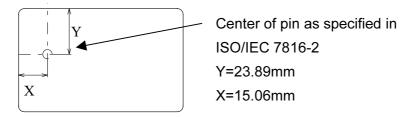

Although there are basically no particular restrictions on the shape and position of the antenna allocation in PICC, the position indicated in "Fig. 5.1-1 Minimum Coupling Area of PICC" shall be included.

Fig. 5.1-1 Minimum Coupling Area of PICC

### (2) Extended Specifications

In order to operate the PICC in four direction (front, back, up, down), the antenna mounting area shall be where the coupling area will be minimum with respect to all directions. The antenna allcation renge is shown with diagonal lines in "Fig. 5.1-2 Antenna Mounting Range".

Fig. 5.1-2 Antenna Mounting Range

#### (3) References

### 5.2 Antenna Resistance Value

(1) Basic Specifications

None

# (2) Extended Specifications

Although resistance values are not particularly specified in this specification, the resistance value shall at least satisfy the specifications specified in the following:

- "8. Power Transmission"

- "9. Communication PCD to PICC"

- "10. Communication PICC to PCD"

- "14. Card Test Methods"

### (3) References

### 5.3 Inductance

### (1) Basic Specifications

None

### (2) Extended Specifications

Although inductance are not particularly specified in this specification, the inductance value shall at least satisfy the specifications specified in the following:

- "8. Power Transmission"

- "9. Communication PCD to PICC"

- "10. Communication PICC to PCD"

- "14. Card Test Methods"

### (3) References

#### 5.4 Resonance Frequency

#### (1) Basic Specifications

None

#### (2) Extended Specifications

The resonance frequencies when using a single PICC and when superimposing two cards are specified.

#### (a) When Using a Single Card

The resonance frequency is preferably 19 MHz or higher, and shall at least satisfy the specifications specified in the following:

- "8. Power Transfer"

- "9. Communication PCD to PICC"

- "10. Communication PICC to PCD"

- "14. Card Test Methods"

Furthermore, in the case of card premised on single card operation, the resonance frequency may be 19 MHz or lower, but considerations must be given to the effects when bringing the card in close proximity of a PCD.

In addition, in the case of using superimposed cards, a resonance frequency that satisfies the specification in "5.4 (2) (b) When Superimposing Two Cards" shall be selected.

Resonance frequency shall be measured using the method specified in the "NOTE" of section "15.3.1 (1) (a) a) 2)".

### (b) When Superimposing Two Cards

The resonance frequency is preferably 13 MHz or higher, and shall at least satisfy the specifications specified in the following:

- "8. Power Transmission"

- "9. Communication PCD to PICC"

- "10. Communication PICC to PCD"

- "14. Card Test Methods"

Resonance frequency shall be measured using the method specified in the "NOTE" of section "15.3.1 (1) (a) a) 2)".

#### (3) References

### 5.5 Material and Production Method

### (1) Basic Specifications

None

### (2) Extended Specifications

Although materials and production methods are not particularly specified in this specification, materials and production methods shall at least satisfy the specifications specified in the following:

- "8. Power Transmission"

- "9. Communication PCD to PICC"

- "10. Communication PICC to PCD"

- "14. Card Test Methods"

### (3) References

#### 6. Card IC Characteristics

Characteristic values including IC power consumption and operating voltage are specified as IC characteristics for PICC. IC characteristics shall be specified with consideration to differences in characteristics due to IC function and production methods.

#### 6.1 Operating Power

#### (1) Basic Specifications

None

#### (2) Extended Specifications

The power supply method, minimum operating power, maximum operating power, maximum input power and input capacity of card ICs are specified.

#### (a) Power Supply Method

The card IC shall operate by receiving power supplied from the PCD through an antenna.

#### (b) Minimum Operating Power

There are no particular specifications for the value of minimum power consumption at which the card IC functions normally. However, the power shall be appropriate for the card IC to operate at the minimum operating magnetic field specified in "14. Card Test Methods".

Section "6.1 (2) (e) Definition of Power Consumption" is applied for the power consumption of the card IC.

#### (c) Maximum Operating Power

There are no particular specifications for the maximum power consumption at which the card ID functions normally. However, the power shall be appropriate for the card IC to operate at the maximum operating magnetic field specified in "14. Card Test Methods".

Section "6.1 (2) (e) Definition of Power Consumption" is applied for the power consumption of the card IC.

#### (d) Maximum Input Power

There are no particular specifications for the value of maximum input power at which the card IC is not destroyed. However, the power shall be that at which the card IC is not destroyed at the maximum applied magnetic field specified in "14. Card Test Methods".

#### (e) Definition of Power Consumption

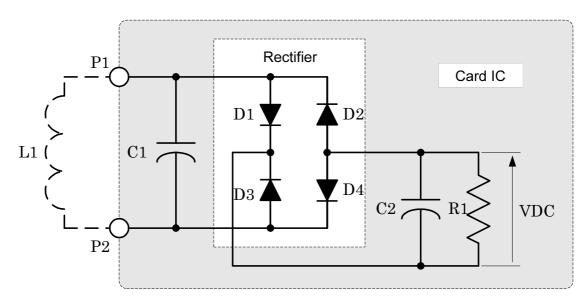

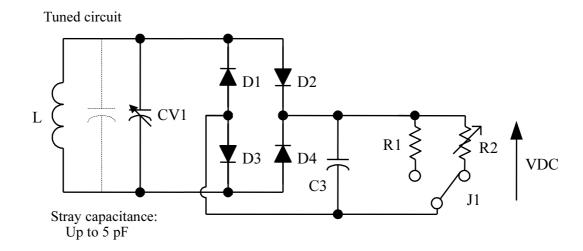

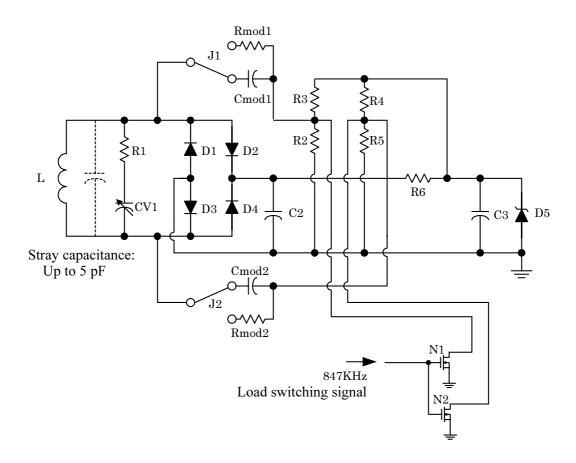

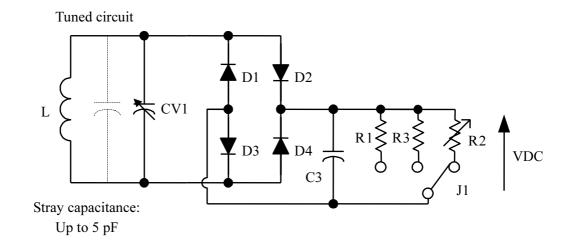

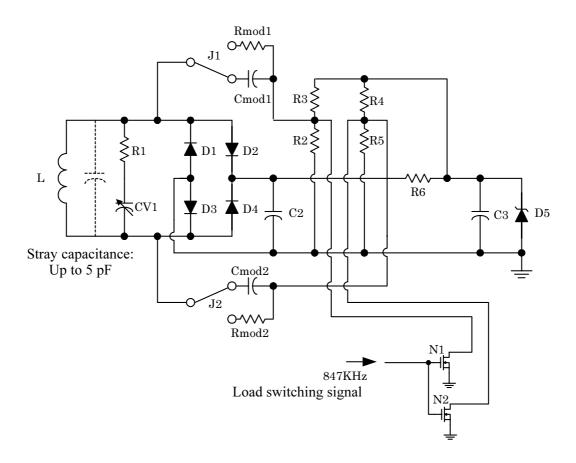

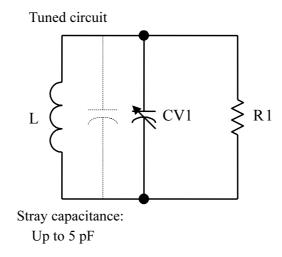

The card IC equivalent circuit and its components are shown in "Fig. 6.1-1 Card IC Equivalent Circuit 1" and "Table 6.1-1 Equivalent Circuit Composition". Card IC power consumption shall be the power that is consumed by load resistor R1 in order to correspond to the Reference PICC circuit drawing specified in Annex D of ISO/IEC 10373-6.

If the rectifier characteristics differ between the card IC and card IC equivalent circuit 1, the power shall be that resulting from converting the card IC rectifier characteristics to the rectifier characteristics of card IC equivalent circuit 1.

Fig. 6.1-1 Card IC Equivalent Circuit 1

Table 6.1-1 Equivalent Circuit Composition

| Symbol         | Components                | Part constant and type      |

|----------------|---------------------------|-----------------------------|

| P1, P2         | Coil connection pad       | -                           |

| C1             | Input capacity            | As per "(f) Input Capacity" |

| D1, D2, D3, D4 | Full wave rectifier diode | Schottky diode              |

|                |                           | (equivalent to BAR43)       |

| C2             | Smoothing capacitor       | Determined by producing     |

|                |                           | manufacturer                |

| R1             | Load resistor             | Determined by producing     |

|                |                           | manufacturer                |

| VDC            | Receiving voltage         | Determined by producing     |

|                |                           | manufacturer                |

| L1             | Antenna                   | -                           |

# (f) Input Capacity

There are no particular specifications for card IC input capacity. However, capacity shall satisfy "5.4 Resonance Frequency" with the antenna connected.

# (3) References

### 6.2 Input Signal

### (1) Basic Specifications

None

### (2) Extended Specifications

The input signal that can be processed normally by the card IC is specified.

The card IC shall be able to normally process the signal specified in "9. Communication PCD to PICC" with the antenna connected. In addition, the tests specified in "14. Card Test Methods" shall be satisfied. However, the antenna connected to the card IC shall satisfy "5. Card Antenna Characteristics".

### (3) References

### 6.3 Output Signal

### (1) Basic Specifications

None

### (2) Extended Specifications

The output signal generated by the card IC is specified.

The card IC shall generate the signal specified in "10. Communication PICC to PCD" with the antenna connected. In addition, the tests specified in "14. Card Test Methods" shall be satisfied. However, the antenna connected to the card IC shall satisfy "5. Card Antenna Characteristics".

### (3) References

#### 7. PCD Antenna Characteristics

Antenna position, shape and other characteristics are specified as PCD antenna characteristics. Antenna characteristics are to be specified with consideration to differences in characteristics due to communication performance and production methods.

#### 7.1 Antenna Position

#### (1) Basic Specifications

None

#### (2) Extended Specifications

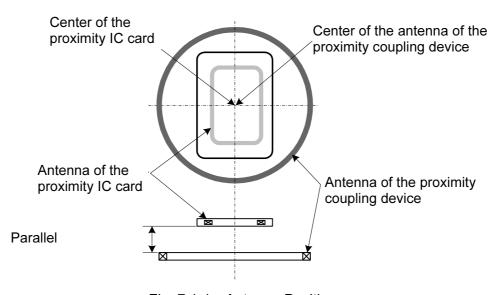

Although there are no particular specifications for antenna position, antenna position shall be decided so as to satisfy communication performance independent of the operating direction (front, back, up, down) of the PICC within the communication range or the coil position. In addition, the antenna shall be aligned in a direction such that the antenna of the PCD and the antenna of the PICC face each other in parallel.

An example of an antenna position of a PCD where the center of the antenna is aligned with the center of the PICC is shown in "Fig. 7.1-1 Antenna Position".

Fig. 7.1-1 Antenna Position

#### (3) References

### 7.2 Antenna Shape

### (1) Basic Specifications

None

### (2) Extended Specifications

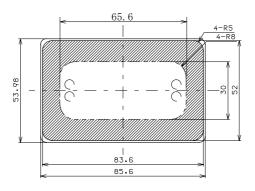

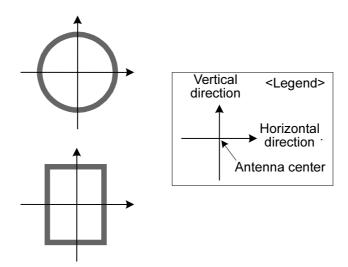

The PCD antenna preferably has a symmetrical shape in order to prevent significant changes in communication performance caused by the direction of operation (front, back, up, down) of the PICC or by the coil position. An example of the antenna shape of a PCD is shown in "Fig. 7.2-1 Antenna Shape".

Fig. 7.2-1 Antenna Shape

### (3) References

### 7.3 Antenna Resistance Value

### (1) Basic Specifications

None

### (2) Extended Specifications

Although resistance values are not particularly specified in this specification, the resistance value shall at least satisfy the specifications specified in the following:

- "8. Power Transmission"

- "9. Communication PCD to PICC"

- "10. Communication PICC to PCD"

- "15. PCD Test Methods"

### (3) References

### 7.4 Inductance

(1) Basic Specifications

None

# (2) Extended Specifications

Although inductance are not particularly specified in this specification, inductance shall at least satisfy the specifications specified in the following:

- "8. Power Transmission"

- "9. Communication PCD to PICC"

- "10. Communication PICC to PCD"

- "15. PCD Test Methods"

### (3) References

### 7.5 Resonance Frequency

### (1) Basic Specifications

None

### (2) Extended Specifications

Although resonance frequency are not particularly specified in this specification, resonance frequency shall at least satisfy the specifications specified in the following:

- "8. Power Transfer"

- "9. Communication PCD to PICC"

- "10. Communication PICC to PCD"

- "15. PCD Test Methods"

### (3) References

## 7.6 Material and Production Method

(1) Basic Specifications

None

## (2) Extended Specifications

Although materials and production method are not particularly specified in this specification, materials and production methods shall at least satisfy the specifications specified in the following:

- "8. Power Transmission"

- "9. Communication PCD to PICC"

- "10. Communication PICC to PCD"

- "15. PCD Test Methods"

## (3) References

## 8. Power Transmission

In addition to specifying power transmission characteristics of the PCD based on ISO/IEC 14443-2, power transmission characteristics of the PCD are specified with consideration to the PCD characteristics and card characteristics as specified in this implementation specification.

# 8.1 Frequency

(1) Basic Specifications

The frequency fc of the RF operating field shall be 13.56 MHz±7kHz.

(2) Extended Specifications

None

(3) References

## 8.2 Operating Magnetic Field

## 8.2.1 PICC Operating Magnetic Field

#### (1) Basic Specifications

## (a) Minimum Operating Magnetic Field (Hmin)

The minimum unmodulated operating field shall be *H*min and has a value of 1.5 A/m (rms).

#### (b) Maximum Operating Magnetic Field (Hmax)

The maximum unmodulated operating field shall be *H*max and has a value of 7.5 A/m (rms).

#### (c) Operating Conditions

A PICC shall operate as intended continually between Hmin and Hmax.

## (d) Maximum Applied Magnetic Field

The PICC must operate normally even after being continuously exposed to a magnetic field strength of an average magnetic field of 10 A/m (rms) at 13.56 MHz. In addition, it must also operate normally even after being exposed for 30 seconds on average to a magnetic field strength of a maximum magnetic field of 12 A/m (rms).

#### (2) Extended Specifications

#### (a) Minimum Operating Magnetic Field (Hmin)

The strength of the minimum operating magnetic field of the PICC is to be 4 A/m (rms) in the non-modulated state.

## (3) References

## 8.2.2 PCD Generated Magnetic Field

#### (1) Basic Specifications

A PCD shall generate a field of at least *H*min and not exceeding *H*max at manufacturer specified positions (operating volume). In addition the PCD shall be capable of powering any signal reference PICC (specified in "15. PCD Test Methods") at manufacuturer specified positions (operating volume).

The PCD shall not generate a field higher than the value specified in section "8.2.1 (d) Maximum Applied Magnetic Field" in any possible PICC position.

Test methods for the PCD operating field are defined in "15. PCD Test Methods".

## (2) Extended Specifications

None

#### (3) References

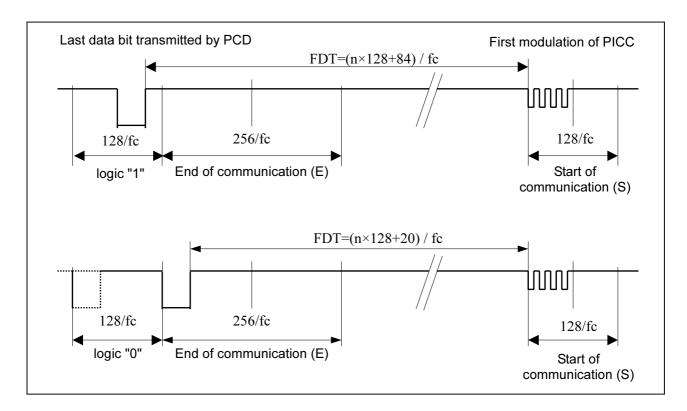

#### 9. Communication PCD to PICC

The modulation method, modulation waveform and encoding method of signal transmission from the PCD to the PICC are specified on the basis of ISO/IEC 14443-2. Type A and Type B communication methods are specified.

- fc: frequency of operating field (carrier frequency).

- Manchester: method of bit coding whereby a logic level during a bit duration is represented by a sequence of two defined physical state of a communication medium. The order of the physical states within the sequence defines the logical state.

- NRZ-L (Non-Return to Zero, L for level): method of bit coding whereby a logic level during a bit duration is represented by one of two defined physical states of a communication medium.

#### 9.1 Communication Signal Interface Type A

#### 9.1.1 Bit Rate

## (1) Basic Specifications

The bit rate for the transmission during initialization and anticollision shall be  $fc/128(\sim 106 \text{ kbit/s})$ .

(2) Extended Specifications

None

(3) References

#### 9.1.2 Modulation

## (1) Basic Specifications

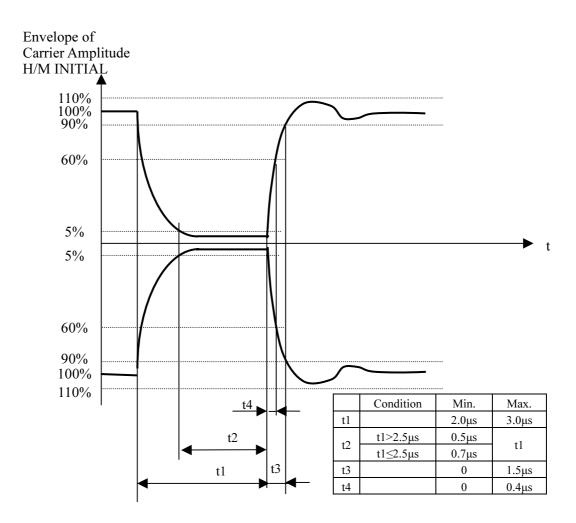

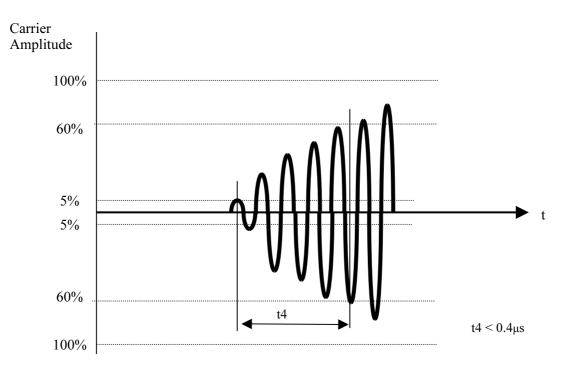

Communication from PCD to PICC for a bit rate of fc/128 shall use the modulation principle of ASK 100% of the RF operating field to create a "Pause" as shown in "Fig. 9.1-1 Pause".

The envelope of the PCD field shall decrease monotonically to less than 5% of its initial value  $H_{\text{INITIAL}}$  and remain less than 5% for more than t2. This envelope shall comply to "Fig. 9.1-1 Pause".

If the envelope of the PCD field does not decrease monotonically, the time between a local maximum and the time of passing the same value before the local maximum shall not exceed 0.5  $\mu$ s. This shall only apply if the local maximum is greater than 5% of  $H_{\text{INITIAL}}$ .

Overshoots shall remain within 90% and 110% of  $H_{\text{INITIAL}}$ .

The PICC shall detect the "End of Pause" after the field exceeds 5% of  $H_{\rm INITIAL}$  and before it exceeds 60% of  $H_{\rm INITIAL}$ .

However, in systems designed to handle only one card at a time, t4 need not be respected.

The waveform of end of pause is shown in "Fig. 9.1-2 Definition of "End of Pause"".

Fig. 9.1-1 Pause

Fig. 9.1-2 Definition of "End of Pause"

# (2) Extended Specifications

None

# (3) References

#### 9.1.3 Bit Representation and Coding

#### (1) Basic Specifications

The following sequences are defined:

- sequence X: after a time of half the bit duration a "Pause" shall occur.

- sequence Y: for the full bit duration no modulation shall occur.

- sequence Z: at the beginning of the bit duration a "Pause" shall occur.

The above sequences shall be used to code the following information:

- logic "1": sequence X

- logic "0": sequence Y with the following two exceptions:

- If there are two or more contiguous "0"s, sequence Z shall be used from the second "0" on.

- If the first bit after a "start of frame" is "0", sequence Z shall be used to represent this and any "0"s which follow directly thereafter.

start of comunication: sequence Z end of communication: logic "0" followed by sequence Y. no information: at least two sequences Y.

(2) Extended Specifications

None

(3) References

# 9.2 Communication Signal Interface Type B

## 9.2.1 Bit Rate

# (1) Basic Specifications

The bit rate for the transmission during initialization and anticollision shall be nominally fc/128(~106 kbit/s). Tolerance and bit boundaries are defined in "12. Anticollision".

# (2) Extended Specifications

None

## (3) References

#### 9.2.2 Modulation

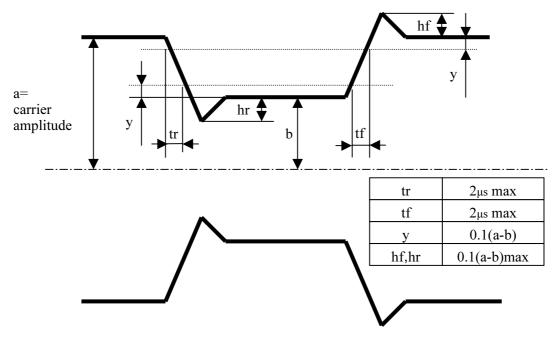

# (1) Basic Specifications

Communication from PCD to PICC shall use the modulation principle of ASK 10% of the RF operating field. The modulation index shall be between 8% and 14%. The modulation waveform shall comply to "Fig. 9.2-1 Type B Modulation Waveform". The rising and falling edges of the modulation shall be monotonic.

Fig. 9.2-1 Type B Modulation Waveform

## (2) Extended Specifications

None

## (3) References

# 9.2.3 Bit Representation and Coding

# (1) Basic Specifications

Bit coding format shall be NRZ-L with logic levels defined as follows:

- Logic "1": carrier high field amplitude(no modulation applied).

- Logic "0": carrier low field amplitude.

# (2) Extended Specifications

None

# (3) References

#### 10. Communication PICC to PCD

The modulation method and encoding method of signal transmission from the PICC to the PCD are specified on the basis of ISO/IEC 14443-2. Type A and Type B communication methods are specified.

The following indicates the terms and abbreviations used in this chapter.

- Subcarrier: signal of frequency fs used to modulate a carrier of frequency fc.

- Bit duration: time during which a logical level is defined, at the end of which a new bit starts.

- Manchester: method of bit coding whereby a logic level during a bit duration is represented by a sequence of two defined physical state of a communication medium. The order of the physical states within the sequence defines the logical state.

- BPSK (Binary Phase Shift Keying): Binary phase shift keying

- fs: Frequency of the subcarrier modulation.

- NRZ-L (Non-Return to Zero. L for level): method of bit coding whereby a logic level during a bit duration is represented by one of two defined physical states of a communication medium.

### 10.1 Communication Signal Interface Type A

#### 10.1.1 Bit Rate

(1) Basic Specifications

The bit rate for the transmission during initialization and anticollision shall be fc/128(~106 kbit/s).

(2) Extended Specifications

None

(3) References

#### 10.1.2 Load Modulation

## (1) Basic Specifications

The PICC shall be capable of communication to the PCD via a inductive coupling area where the carrier frequency is loaded to generate a subcarrier with frequency fs. The subcarrier shall be generated by switching a load in the PICC. The load modulation amplitude shall be at least  $30/H^{1}$ ,  $^{2}$  (mVpeak) when measured as described in ISO/IEC 10373-6, where H is the (rms) value of magnetic field strength in A/m.

## (2) Extended Specifications

None

## (3) References

# 10.1.3 Subcarrier

# (1) Basic Specifications

The frequency fs of the subcarrier shall be fc/16 ( $\sim 847 kHz$ ). Consequently, during initialization and anticollision, one bit period is equivalent to 8 periods of the subcarrier.

# (2) Extended Specifications

None

# (3) References

## 10.1.4 Subcarrier Modulation Method

# (1) Basic Specifications

Every bit period shall start with a defined phase relation to the subcarrier. The bit period shall start with the loaded state of the subcarrier.

The subcarrier is modulated using On/Off keying with the sequence defined in "10.1.5 Bit Representation and Coding".

# (2) Extended Specifications

None

# (3) References

#### 10.1.5 Bit Representation and Coding

#### (1) Basic Specifications

The following sequences are defined:

- sequence D: the carrier shall be modulated with the subcarrier for the first half (50%) of the bit duration

- sequence E: the carrier shall be modulated with the subcarrier for the second half (50%) of the bit duration.

- Sequence F: the carrier is not modulated with the subcarrier for one bit duration.

Bit coding shall be Manchester with the following definitions:

- logic"1": sequence D

- logic"0": sequence E

- start of communication: sequence D

- end of communication: sequnece F

- no information: no subcarrier (Sequence F)

### (2) Extended Specifications

None

## (3) References

# 10.2 Communication Signal Interface Type B

# 10.2.1 Bit Rate

# (1) Basic Specifications

The bit rate for the transmission during initialization and anticollision shall be nominally fc/128( $\sim$ 106 kbit/s).

# (2) Extended Specifications

None

# (3) References

#### 10.2.2 Load Modulation

# (1) Basic Specifications

The PICC shall be capable of communication to the PCD via a inductive coupling area where the carrier frequency is loaded to generate a subcarrier with frequency fs. The subcarrier shall be generated by switching a load in the PICC.

The load modulation amplitude shall be at least  $30/H^{1,2}$  (mVpeak) when measured as described in ISO/IEC10373-6, where H is the (rms) value of magnetic field strenfh in A/m.

## (2) Extended Specifications

None

## (3) References

#### 10.2.3 Subcarrier

# (1) Basic Specifications

The frequency fs of the subcarrier shall be fc/16 (~847kHz). Consequently, during initialization and anticollision, one bit period is equivalent to 8 periods of the subcarrier. The PICC shall generate a subcarrier only when data is to be transmitted.

# (2) Extended Specifications

None

## (3) References

#### 10.2.4 Subcarrier Modulation

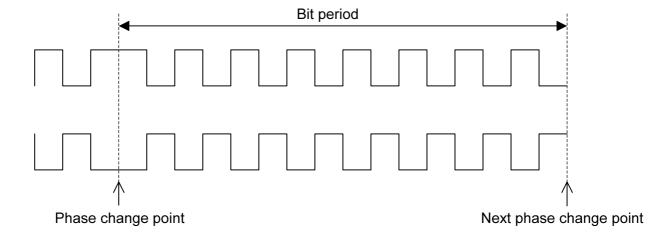

# (1) Basic Specifications

The subcarrier shall be BPSK modulated, see example in "Fig. 10.2-1 Allowed phase shifts" with BPSK modulation. Phase shifts shall only occur at nominal position of rising or falling edges of the subcarrier.

Fig. 10.2-1 Allowed Phase Shifts

(2) Extended Specifications

None

(3) References

#### 10.2.5 Bit Representation and Coding

## (1) Basic Specifications

Bit coding shall be NRZ-L where a change of logic level shall be denoted be a phase shift (180°) of the subcarrier.

The initial logic level for NRZ-L at the start of a PICC frame shall be established by the following sequence:

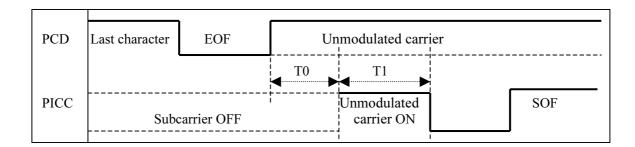

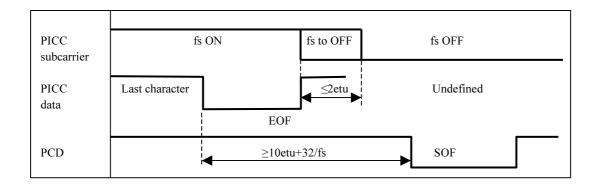

After any command from the PCD a guard time TR0 shall apply in which the PICC shall not generate a subcarrier. TR0 shall be greater than 64/fs.

The PICC shall then generate a subcarrier with no phase tradition for a synchronization time TR1. This establishes a subcarrier phase reference  $\Phi$ 0. TR1shall be greater than 80/fs.

This initial phase state  $\Phi 0$  of the subcarrier shall be defined as logic "1" so that the first phase transition represents a change from logic "1" to logic "0".

Subsequently the logic level is defined according to the subcarrier phase reference  $\Phi$ 0:

```

Φ0: represents logic"1". Φ0 + 180^\circ: reperesents logic "0".

```

#### (2) Extended Specifications

None

#### (3) References

# 11. Polling

Polling for detecting existence of a PICC capable of communicating with the PCD is specified based on ISO/IEC 14443-3. Polling methods compatible with both type A and type B communication methods are specified.

The following indicates the terms and abbreviations used in this chapter.

- REQA (Request Command, Type A): Request command for a Type A PICC

- REQA (Request Command, Type B): Request command for a Type B PICC

- ATQ (Answer To Read): Response signal from PICC.

Furthermore, the PCD described in this chapter includes external devices.

#### (1) Basic Specifications

In order to detect PICCs which are in the operating field, a PCD shall send repeated Request commands. The PCD shall send REQA and REQB described in "12. Anticollision" and in adtion may send other commands described in "12.5 Type A Timeslot - Initialization and Anticollision".

When a PICC is exposed to an unmodulated operating field it shall be able to accept within 5ms (see "8. Power Transfer").

#### More specifically:

- EXAMPLE 1 When a PICC Type A receives and Type B command it shall be able to accept a REQA within 5ms of unmodulated operating field.

- EXAMPLE 2 When a PICC Type B receives any Type A command it shall be able to accept a REQB within 5ms of unmodulated operating field.

### (2) Extended Specifications

None

## (3) References

The request commands used for polling may use the encoding system described in "12.5 Type A Timeslot - Initialization and Anticollision" and REQB having an optional method. (For further details, refer to References of section "12.2.4(3)" of "12.2 Type B Initialization and Anticollision Processing".)

#### 12. Anticollision

Anticollision is specified on the basis of ISO/IEC 14443-3 for acquiring identification information of PICC where multiple PICCs capable of communicating with the PCD are present. Communication methods are specified for both type A and type B.

#### (1) Terms Used in this Section

#### - Anticollision Loop

algorithm used to prepare for dialogue between PCD and one or more PICCs out of the total number of PICCs responding to a request command

#### - Bit Collision Detection Protocol

Processing method which gives significance to bit units within a frame. Collision occurs when two or more PICCs send complementary bit patterns to the PCD. In the case of type A PICCs, the bit pattern overlaps and the carrier is modulated with the subcarrier for the entire bit period (100%). PCD recognizes the IDs of all PICCs in order while detecting colliding bits.

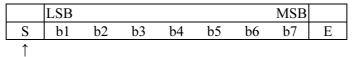

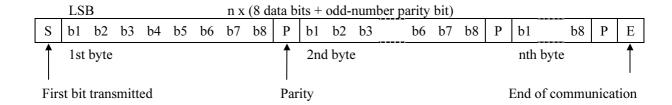

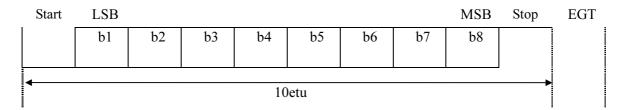

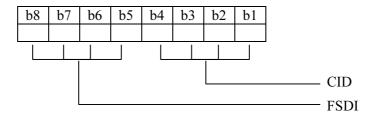

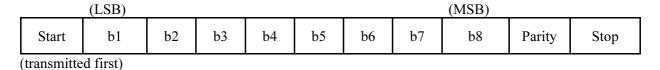

#### - Byte

8 bits of data designated b8 to b1, from the most significant bit (MSB, b8) to the least significant bit (LSB, b1)

#### - Collision

transmission by two PICCs in the same PCD energizing field and during the same time period, such that the PCD is unable to distinguish from which PICC the data originated.

### - elementary time unit

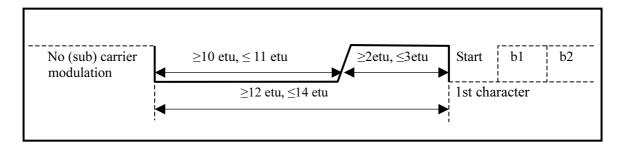

etu

for "12. Anticollision", one etu is defined as 1 etu=128/fc (i.e. 9.4 µs nominal)

#### - Frame

sequence of data bits and optional error detection bits, with frame delimiters at start and end

## - Higher layer protocol

protocol layer ( not described in that makes use of the protocol layer defined in to transfer information belonging to the application or higher layers of protocol that is not described in "12. Anticollision".

# - Timeslot protocol

method whereby a PCD establishes logical channels with one or more PICCs of Type B, which makes use of timeslot allocation for PICC response

#### - Unique Identifier

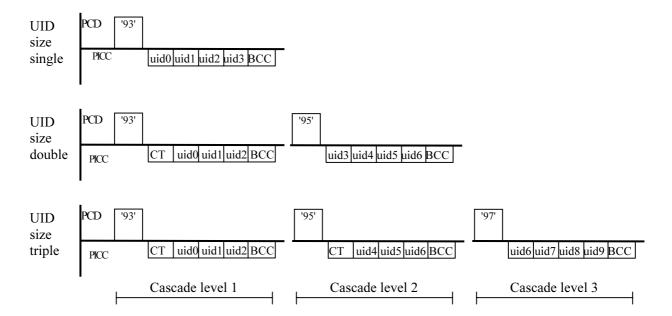

UID is the number used for anticollision processing of type A cards.

## (2) Symbols Used in this Section

#### - AFI Application field identifier

Preliminary card screening standard according to the application field.

- APa Parameter used with ATQB- APc Parameter used with ATTRIB

- APf Anticollosion Prefix f, used in REQB

- APn Anticollision Prefix n, used in Slot-MARKER Command

- ATA Response to ATTRIB

- ATQ Request acknowledgment signal

- ATQA Answer To Request, Type A

- ATQB Answer To Request, Type B

- ATTRIB PICC selection command

- BCC UID CLn check byte, calculated as exclusive-or over the 4 previous bytes

- CLn Cascade Level n (3 ≥ n ≥ 1)

CT Cascade Tag (value is '88')

- CRC\_A Cyclic Redundancy Check error detection code A- CRC B Cyclic Redundancy Check error detection code B

- DESEL Deselect command

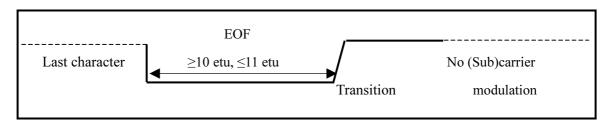

- E End of communication, Type A

- EGT Extra Guard Time- EOF End Of Frame

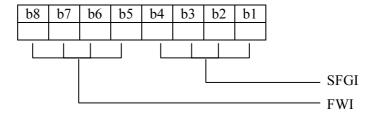

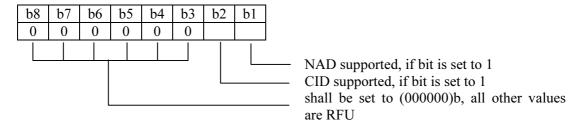

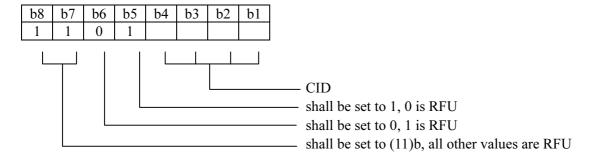

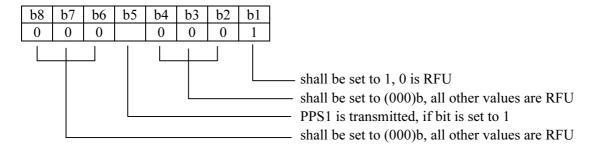

- etu Elementary time unitFGT Frame guard time

- fc Carrier frequency (13.56 MHz)fs Subcarrier frequency (fc/16)

- ID IDentification number

- INF INFormation field belonging to higher layer

- LSB Least significant bitMSB Most significant bit

- N Number of anticollision slots or PICC response probability in each slot

- n Variable integer value as defined in the specific clause

- NAD Node address

- NVB Number of Valid Bits

- P Odd Parity bit

| - PARAM | Attribute information parameter                                                     |  |  |

|---------|-------------------------------------------------------------------------------------|--|--|

| - PCD   | Proximity coupling device for proximity IC card (including upper devices)           |  |  |

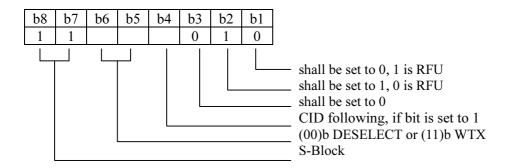

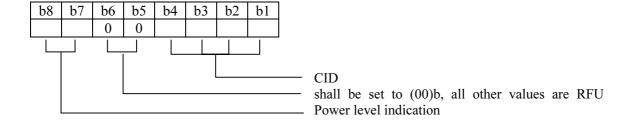

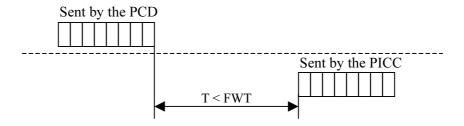

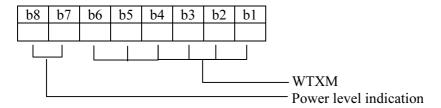

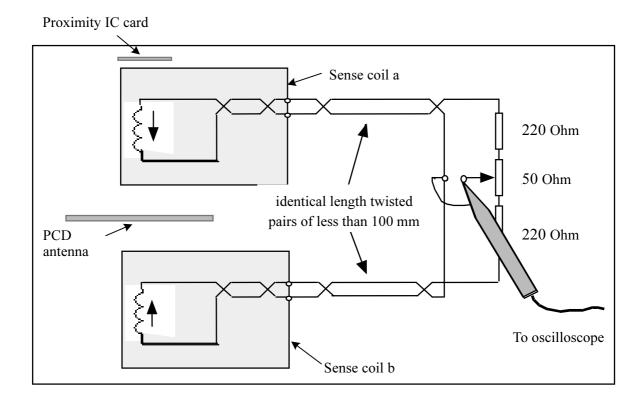

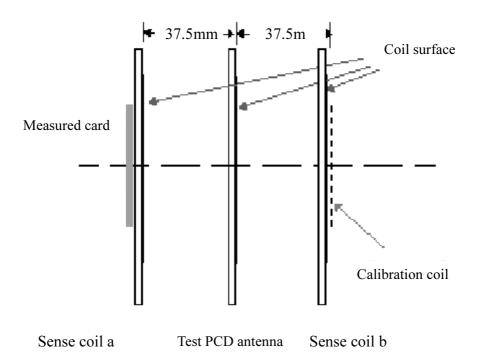

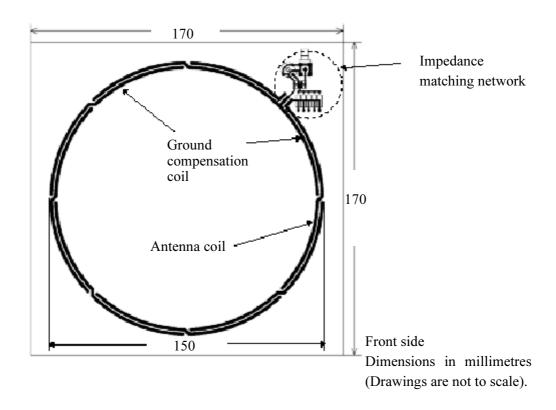

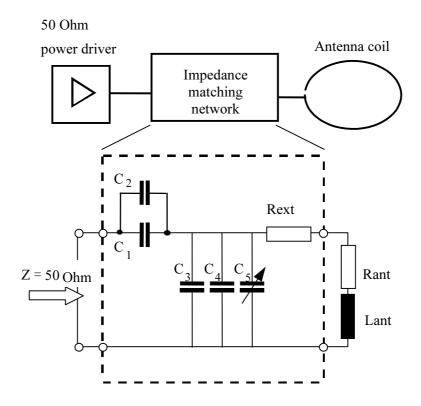

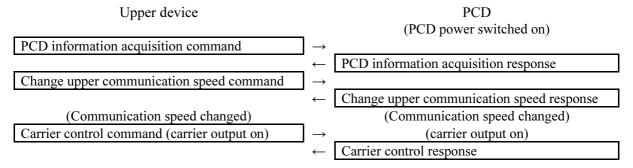

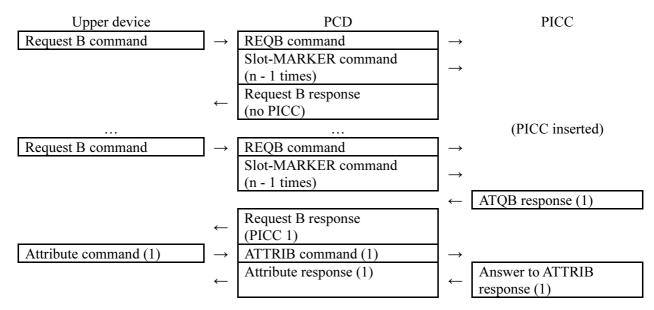

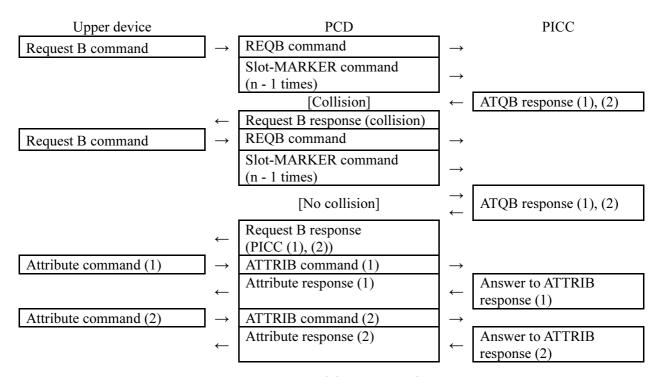

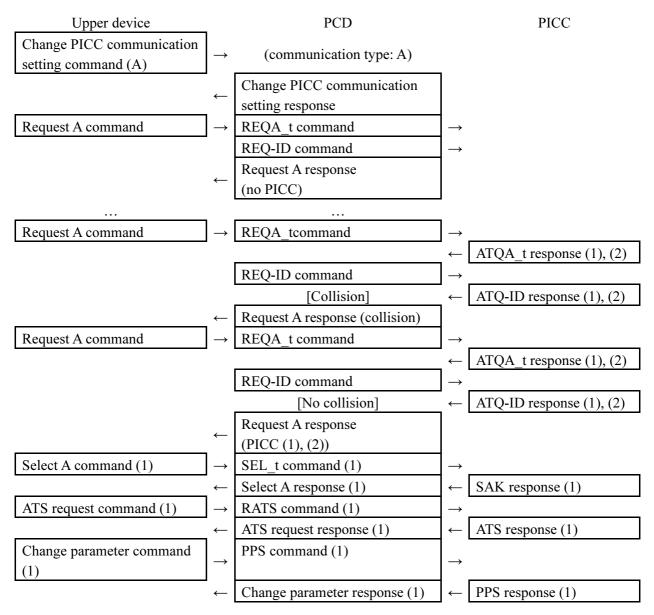

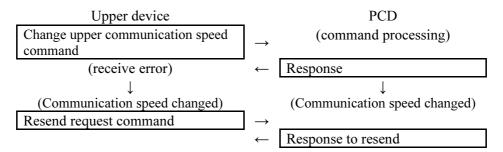

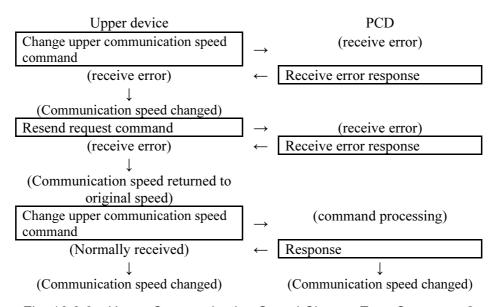

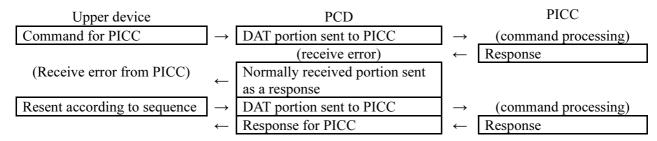

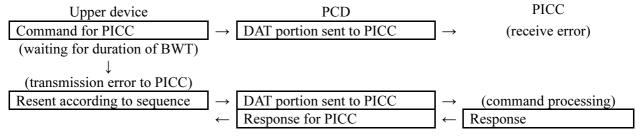

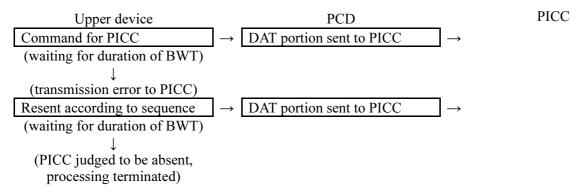

| - PICC  | Proximity Card                                                                      |  |  |